# SESHASAYEE INSTITUTE OF TECHNOLOGY(AUTONOMOUS) ARIYAMANGALAM,TRICHY – 10

#### **DIPLOMA IN ELECTRICAL & ELECTRONICS ENGINEERING**

EAR/SEMESTER : III/V

COURSE CODE: 2E5402.1 COURSE TITLE: MICROCONTROLLER

#### UNIT - I

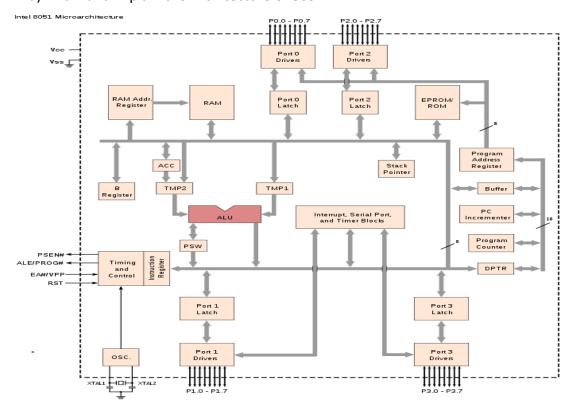

a) Draw and Explain the Architecture of 8051.

(80)

#### **Functional Description Of Each Block:**

- a) <u>Accumulator: (Acc)</u> Acc is an 8 bit special function register. It acts an operand register. Result is temporarily stored in this register. It is used in parallel I/O transfer.

- b) **B Register**: B register is 8 bit SFR. It is used during multiply and divide operations.

For other operations, it can be used as a scratchpad register.

- c) <u>Program Status Word (PSW)</u>: PSW register is 8 bit SFR. It contains program status information. It is also used to select any one of the required register bank.

- d) <u>Stack Pointer (SP):</u> It is 8 bit register. It is used to point the stack memory. The stack may reside in anywhere in on-chip memory. It is incremented before data is stored during PUSH & CALL instructions. After reset SP is initialized to 07h. This causes the stack begin at location 08h.

- e) <u>Data Pointer (DPTR)</u>: It is 16 bit register. It may be manipulated as a 16 bit register or as two independent 8 bit registers. Its function is to hold a 16 bit address. This register is used for external reference.

- f) Port 0 to Port 3: Each port contains separate address. Using this address, User can communicate with these ports. Each port contains latch, output driver & input buffer.

- g) <u>Serial Data Buffer</u>: Serial data buffer contains two independent registers of a transmit buffer register and a receiver buffer register.

- Transmit buffer is a parallel in and Serial out register.

- Receiver buffer is a Serial in and parallel out register.

- When data is moved to SBUF, it goes to transmit buffer .

- When data is moved from SBUF, it comes from the receive buffer.

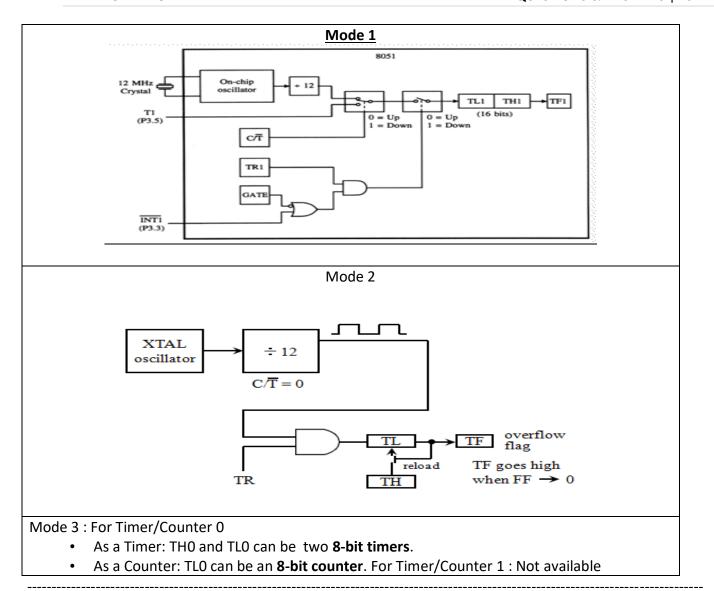

- h) <u>Timer Registers</u>: Register pairs (TH0,TL0) & (TH1,TL1) are the two 16 bit counting registers for Timer/Counter 0 and 1 respectively.

- i) <u>Control Registers</u>: The special function registers IP,IE, TMOD, TCON SCON and PCON contain control and ststus information for interrupts, timer/counters and serial port.

- j) <u>Timing & Control Unit</u>: This unit derives an necessary timing and control signals required for the internal operations of the circuit. It derives control signals required for contolling the external system bus. The interrupt, serial port and timer circuits are controlled by the control signals generated by timing & control unit.

- k) <u>Oscillator</u>: This circuit generates the basic timing clock signal for the operation of the circuit using crystal oscillator.

- l) <u>Instruction Register</u>: This register decodes the opcode of an instruction to be executed and gives information to the timing & control unit, and to generate necessary signals for the execution of the instruction.

- m) **EPROM & Program Address Register:** These blocks provide an onchip EPROM and a Mechanism to internally address it.

- n) RAM & RAM address register: These blocks provide an onchip RAM and a mechanism to internally address it.

- o) <u>ALU:</u> The **Arithmetic And Logic Unit** performs 8 bit arithmetic and logical operations over the operands held by the temporary registers TMP 1 and TMP 2. User cannot access these temporary registers

- p) <u>SFR Register Banks</u>: It is a set of registers, which can be addressed using their respective addresses which lie in the range 80h to FFh.

\_\_\_\_\_\_

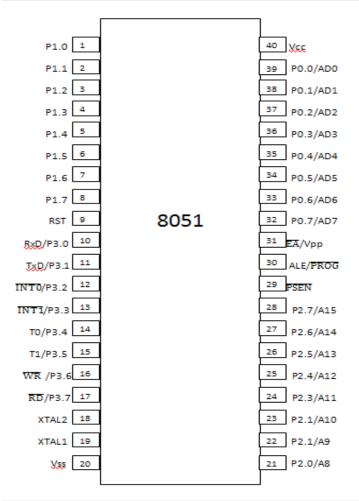

Draw the pin Diagram of 8051 and explain the function of each pin (08)

<u>Pin Description of 8051 micro controller</u> Vcc &Vss : Power supply Signals

**Port 0(p0.0 to p0.7):** It is 8-bit bi-directional I/O port. It is bit/ byte addressable. During external memory access, it functions as multiplexed data and low-order address bus AD0-AD7

**Port 1(p1.0 to p1.7):** It is 8-bit bi-directional I/O port. It is bit/ byte addressable. When logic 1 is written into port latch then it work as input mode. It functions as simply I/O port and it does not have any alternative function.

**Port 2(p2.0 to p2.7):** It is 8-bit bi-directional I/O port. It is bit/ byte addressable. During external memory access it functions as higher order address bus (A8-A15).

**Port 3(p3.0 to p 3.7):** It is 8-bit I/O port. In an alternating function each pins can be used as a special function I/O pin.

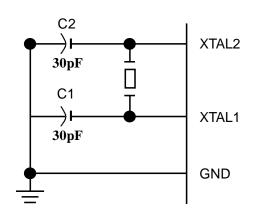

**XTAL 1 and XTAL 2:** These are two I/P line for on-chip oscillator and clock generator circuit.

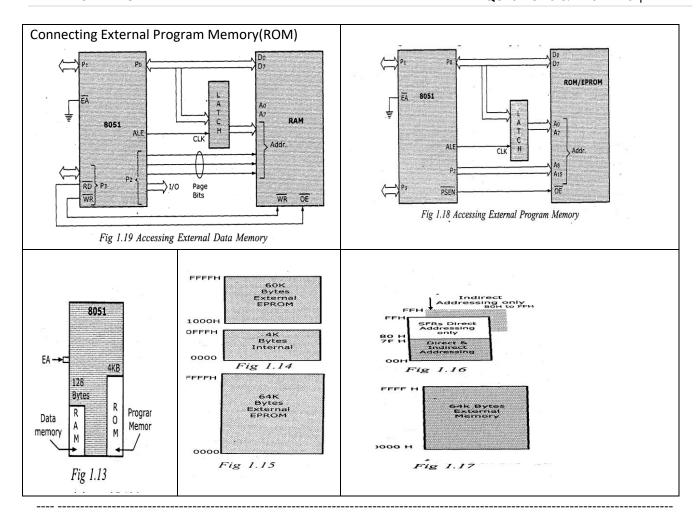

(EA)'.../ VPP: External Access: It is an active low I/P to 8051  $\mu$ c. when (EA)'= 0, then 8051  $\mu$ c access from external program memory (ROM) only.

When (EA)'= 1, then it access internal and external program memories (ROMS).

(PSEN)': Program Store Enable: It is active low O/P signal. It is used to enable external program memory (ROM). When (PSEN)'=0, then external program memory becomes enable and μc read content of external memory location. Therefore it is connected to (OE)' of external ROM. It is activated twice every external ROM memory cycle.

ALE-Address latch enable: It is active high O/P signal. When it goes high, external address latch becomes enabling and lower address of external memory (RAM or ROM) latched into it. Thus it separates AO-A7 address from ADO- AD7. It

provides properly timed signal to latch lower byte address. The ALE is activated twice in every machine cycle.

**RESET:** It is active high I/P signal. It should be maintained high for at least two machine cycle while oscillator is running then 8051  $\,\mu c$  resets, i.e. It clears the following registers: A,B,PSW

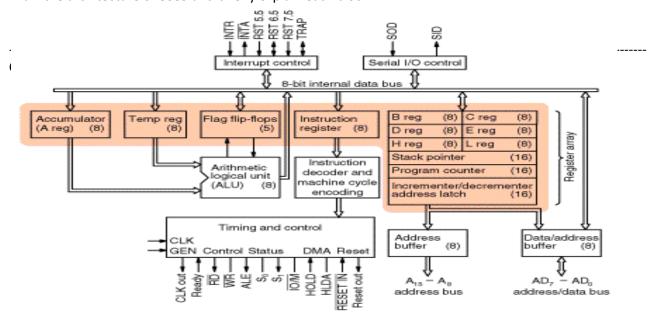

Draw the architecture of 8085 and briefly explain each block.

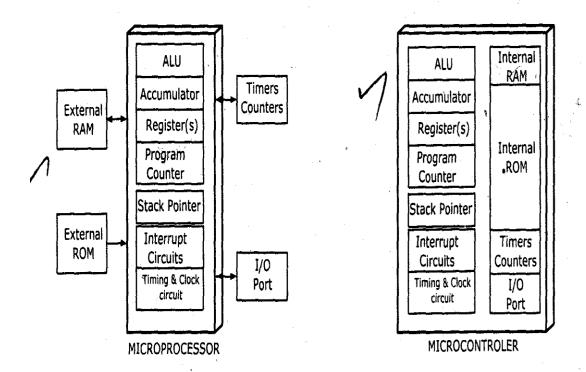

#### COMPARE MICROPROCESSOR & MICROCONTROLLER

# COMPARING MICROPROCESSOR AND MICROCONTROLLER

| Sl.No. | Microprocessor (mP)                      | Microcontroller (mC)                   |

|--------|------------------------------------------|----------------------------------------|

| 1.     | It is intended tobe general - purpose    | It is intended to be special purpose   |

| ,      | digital computers                        | digital controllers.                   |

| 2.     | It contains CPU memory addressing        | It contains CPU as well as timers,     |

|        | circuits and interrupt, handling circuit | parallel and serial I/O and internal   |

|        | ·                                        | RAM and ROM                            |

| 3.     | Microprocessor have many operational     | It may have many bit handling          |

|        | codes (opcodes) for moving data from     | instructions.                          |

|        | external memory to the CPU.              |                                        |

| 4.     | It has one or two types of bit           | It has many bit handling instructions. |

|        | handling instructions.                   |                                        |

| 5.     | Microprocessor is concerned with         | Microcontroller is concerned with the  |

|        | rapid movement of code and data          | movement of bits within the chip.      |

|        | from external address to the chip        |                                        |

| 6.     | Microprocessor must have many            | Microcontroller can function as a      |

| -      | additional parts peripherals to          | computer with the addition of no       |

|        | function as a computer                   | external digital parts.                |

#### **APPLICATIONS**

| Applica                                                | Application of Microcontroller                   |  |  |  |  |  |  |

|--------------------------------------------------------|--------------------------------------------------|--|--|--|--|--|--|

| Industrial Control Devices:                            | Day to Day Life Devices:                         |  |  |  |  |  |  |

| <ul> <li>Industrial instrumentation devices</li> </ul> | Light sensing & controlling devices              |  |  |  |  |  |  |

| Process control devices                                | Temperature sensing and controlling devices      |  |  |  |  |  |  |

|                                                        | Fire detection & safety devices                  |  |  |  |  |  |  |

|                                                        | Security Alarms                                  |  |  |  |  |  |  |

|                                                        | • In Computers-> Modems and Keyboard Controllers |  |  |  |  |  |  |

| Metering & Measurement Devices:                        | electronic equipments :                          |  |  |  |  |  |  |

| Volt Meter                                             | Mobile Phones                                    |  |  |  |  |  |  |

| Measuring revolving objects                            | Auto Mobiles                                     |  |  |  |  |  |  |

| Current meter                                          | CD/DVD Players                                   |  |  |  |  |  |  |

| Hand-held metering systems                             | Washing Machines                                 |  |  |  |  |  |  |

|                                                        | • Cameras                                        |  |  |  |  |  |  |

|                                                        | Microwave Oven.                                  |  |  |  |  |  |  |

\_\_\_\_\_

List down the applications of microcontroller.

| Keyboard     | MP3 music players          | Electronic toys        |

|--------------|----------------------------|------------------------|

| Printer      | Data switches              | Washing machines       |

| video game   | Embedded memories to keep  | Stepper motor control  |

| Mobile phone | Domestic (home) appliances | Traffic control        |

| Automotive   | Small business system      | DC motor speed control |

| Office       | Xerox copier               | Inverters              |

The <u>use of microcontroller in various fields</u> such as automobile, aeronautics, space, robotics, electronics, defense application, mobile communications, rail transport, industrial processing, and medical applications is rapidly increasing.

There are numerous applications of 8051 microcontroller in science and technology and a few more of them can be listed as below

- Prepaid energy meter using microcontroller and GSM modem

- Transformer/Generator health monitoring remotely over internet

- Power theft detection and intimation to control room using GSM

- Controlling remote industrial plant using SCADA

- · Avoiding excessive electric bills for industries and commercial establishments

- Induction motor speed control using Arduino

- Density based traffic signal system controlled using a smartphone

- Virtual display of messages using propeller drive LEDs

- Digital sensor based temperature control

- High power dual converter using a pair of SCR bridge

- LAN like setup of multiple microcontrollers

- Positioning of dish antenna using the remote

- I2C protocol based auto dialing on burglary detection

- Energy Management: Competent measuring device systems aid in calculating energy consumption in domestic and industrialized applications. These meter systems are prepared competent by integrating microcontrollers.

- **Touch screens:** A high degree of microcontroller suppliers integrate touch sensing abilities in their designs. Transportable devices such as media players, gaming devices & cell phones are some illustrations of micro-controller integrated with touch sensing screens.

- Automobiles: The microcontroller 8051 discovers broad recognition in supplying automobile solutions. They are extensively utilized in hybrid motor vehicles to control engine variations.

In addition, works such as cruise power and anti-brake mechanism has created it more capable with the amalgamation of micro-controllers.

- Medical Devices: Handy medicinal gadgets such as glucose & blood pressure monitors bring

into play micro-controllers, to put on view the measurements, as a result, offering higher

dependability in giving correct medical results.

Explain the memory organization of 8051 microcontroller.

(08)

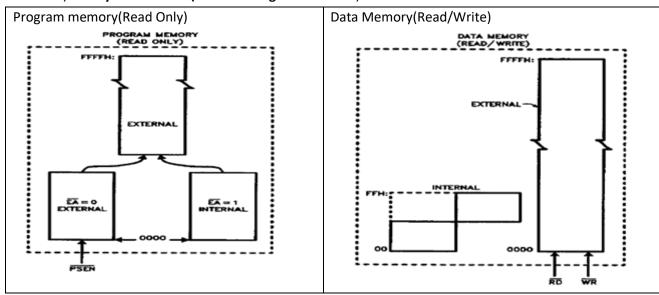

**MEMORY ORGANIZATION:** The 8051 architecture provides both on chip memory as well as off chip memory expansion capabilities. It supports several distinctive 'physical' address spaces, functionally EA separated at the hardware level by different addressing mechanisms, read and write controls signals or both. The 8051 has on chip memory of 4 Kbytes of internal Program Memory and 128 bytes of internal Data memory. It can access upto 64 K program memory and 64Kdata memory.

The 3 different address spaces of 8051

i) 64 Kbyte program memory ii) 64 Kbyte external data memory iii) 256 byte internal data memory. **Internal Data Memory** (256bytes) is divided into two physically separate and distinct blocks.

- i) 128 Bytes Internal RAM Area. This area is further divided into three.

- a) Four register banks [each bank has eight 8 bit registers] (address range 00 1Fh)

- b) 16 bytes bit addressable locations (address range 20h 2Fh)

- c) 80 bytes byte addressable locations (address range 30h 7Fh)

- ii) 128 Bytes SFR Area (address range 80h 0FFh)

Explain internal memory Organization of 8051 with neat diagram Internal data memory (256bytes) is divided into two physically separate and distinct blocks.

- i) 128 bytes internal RAM area. This area is further divided into three.

- a) Four register banks [each bank has eight 8 bit registers] (address range 00 1Fh)

- b) 16 bytes bit addressable locations (address range 20h 2Fh)

- c) 80 bytes byte addressable locations (address range 30h 7Fh)

- ii) 128 bytes SFR area ( address range 80h 0FFh )

#### **Bit Addressable RAM**

| RAM     |    |    |      |       |      |       |    |    |   |   |                           |                           |   |         |          |    |    |      |     |     |    |     |

|---------|----|----|------|-------|------|-------|----|----|---|---|---------------------------|---------------------------|---|---------|----------|----|----|------|-----|-----|----|-----|

| Byte    |    |    |      |       |      |       |    |    |   |   |                           |                           |   | Byte    |          |    |    |      |     |     |    |     |

| address |    |    |      | 3ita  | ıddr | ess   |    |    |   |   |                           |                           | 4 | address |          |    | E  | 3ita | ddr | ess |    |     |

| 27      | 3F | 3E | 3D   | 3C    | 3В   | 3A    | 39 | 38 |   |   | S                         |                           |   | 7F      |          |    |    |      |     |     |    |     |

| 26      | 37 | 36 | 35   | 34    | 33   | 32    | 31 | 30 |   | L | Bit-addressable locations |                           |   |         |          |    |    |      |     |     |    |     |

| 25      | 2F | 2E | 2D   | 2C    | 2В   | 2A    | 29 | 28 |   |   | 100                       |                           |   |         |          |    |    |      |     |     |    |     |

| 24      | 27 | 26 | 25   | 24    | 23   | 22    | 21 | 20 |   |   | ple                       |                           |   |         |          |    |    | Gene |     |     |    | - 1 |

| 23      | 1F | 1E | 1D   | 1C    | 1B   | 1A    | 19 | 18 |   | ſ | SSS                       |                           |   |         |          |    | I  | RA   |     |     |    |     |

| 22      | 17 | 16 | 15   | 14    | 13   | 12    | 11 | 10 |   |   | dg.                       |                           |   |         |          |    |    |      |     |     |    |     |

| 21      | 0F | 0E | 0D   | 0C    | 0B   | 0A    | 09 | 08 |   |   | ==                        |                           |   |         |          |    |    |      |     |     |    |     |

| 20      | 07 | 06 | 05   | 04    | 03   | 02    | 01 | 00 |   |   | m                         |                           |   | 30      |          |    |    |      |     |     |    |     |

| 1F      |    |    |      | -     |      |       |    |    |   |   |                           |                           | Γ | 2F      | 7F       | 7E | 7D | 7C   | 7В  | 7A  | 79 | 78  |

| 18      |    |    |      | Bar   | ik 3 |       |    |    |   |   |                           | .00                       | ı | 2E      | 77       | 76 | 75 | 74   | 73  | 72  | 71 | 70  |

| 17      |    |    |      | D     | ık 2 |       |    |    | 1 |   |                           | ocal                      | ı | 2D      | 6F       | 6E | 6D | 6C   | 6B  | 6A  | 69 | 68  |

| 10      |    |    |      | Баг   | IK Z |       |    |    |   |   |                           | je l                      | ı | 2C      | <b>6</b> | 66 | 65 | 64   | 63  | 62  | 61 | 60  |

| OF      |    |    |      | Bar   | JL I |       |    |    | 1 |   |                           | ssal                      | 1 | 2B      | 5F       | 5E | 5D | 5C   | 5В  | 5A  | 59 | 58  |

| 08      |    |    |      | Бан   |      |       |    |    |   |   |                           | dre                       | ١ | 2A      | 57       | 56 | 55 | 54   | 53  | 52  | 51 | 50  |

| 07      |    |    | Def  | ault  | reg  | ister | -  |    | 1 |   |                           | Bit-addressable locations |   | 29      | 4F       | 4E | 4D | 4C   | 4B  | 4A  | 49 | 48  |

| 00      |    | ŀ  | bank | c for | RO   | ⊢R7   | 7  |    |   |   |                           | B                         | ı | 28      | 47       | 46 | 45 | 44   | 43  | 42  | 41 | 40  |

|         |    |    |      |       |      |       |    |    | - |   |                           |                           | L | -       |          |    |    |      |     |     |    |     |

#### Bit Addressable RAM

#### DATA MEMORY (RAM) INTERNAL DATA ADDRESS SPACE

| 0xFF                 | Upper 128 RAM<br>(Indirect Addressing<br>Only) | Special Function<br>Register's<br>(Direct Addressing Only) |

|----------------------|------------------------------------------------|------------------------------------------------------------|

| 0x80<br>0x7F         | (Direct and Indirect<br>Addressing)            | Lower 128 RAM                                              |

| 0x30<br>0x2F<br>0x20 | Bit Addressable                                | (Direct and Indirect<br>Addressing)                        |

| 0x1F<br>0x00         | General Purpose<br>Registers                   |                                                            |

| Byte    |                         |      | Byte    |                         |      |

|---------|-------------------------|------|---------|-------------------------|------|

| address | Bit address             |      | address | Bit address             |      |

| 98      | 9F 9E 9D 9C 9B 9A 99 98 | SCON | FF      |                         |      |

|         |                         |      | F0      | F7 F6 F5 F4 F3 F2 F1 F0 | В    |

| 90      | 97 96 95 94 93 92 91 90 | Pl   |         |                         |      |

|         |                         |      | E0      | E7 E6 E5 E4 E3 E2 E1 E0 | ACC  |

| 8D      | not bit addressable     | THI  |         |                         |      |

| 8C      | not bit addressable     | TH0  | D0      | D7 D6 D5 D4 D3 D2 - D0  | PSW  |

| 8B      | not bit addressable     | TL1  |         |                         |      |

| 8A      | not bit addressable     | TL0  | B8      | BCBBBAB9B8              | IP   |

| 89      | not bit addressable     | TMOD |         |                         |      |

| 88      | 8F 8E 8D 8C 8B 8A 89 88 | TCON | B0      | B7 B6 B5 B4 B3 B2 B1 B0 | P3   |

| 87      | not bit addressable     | PCON |         |                         |      |

|         |                         |      | A8      | AF ACABAA A9 A8         | ΙE   |

| 83      | not bit addressable     | DPH  |         |                         |      |

| 82      | not bit addressable     | DPL  | A0      | A7 A6 A5 A4 A3 A2 A1 A0 | P2   |

| 81      | not bit addressable     | SP   |         |                         |      |

| 80      | 87 86 85 84 83 82 81 80 | P0   | 99      | not bit addressable     | SBUF |

XTAL Connection to 8051

Find the machine cycle for

- (a) XTAL = 11.0592 MHz

- (b) XTAL = 16 MHz.

#### Solution:

- (a) 11.0592 MHz / 12 = 921.6 kHz; machine cycle =  $1 / 921.6 \text{ kHz} = 1.085 \mu \text{s}$

- (b) 16 MHz / 12 = 1.333 MHz; machine cycle = 1/1.333 MHz =  $0.75 \mu s$

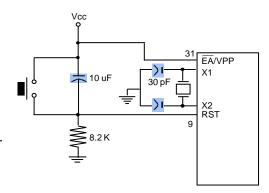

Power-On RESET

- RST (pin 9) : reset

- (i) input pin and active high (normally low).

The high pulse must be high at least 2 machine cycles.

(ii)power-on reset. Upon applying a high pulse to RST, the microcontroller will reset and all values in registers will be lost. Reset values of some 8051 registers

(A)

$$\leftarrow$$

00 ;(SP)  $\leftarrow$  07

(iii)power-on reset circuit -as shown in figure

List down SFRs with their byte and bit addresses. (80)

SPECIAL FUNCTION REGISTERS (SFRS): Special Function Registers (SFRs) are a sort of control table used for running and monitoring the operation of the microcontroller. Each of these registers as well as each bit they include, has its name, address in the scope of RAM and precisely defined purpose

such as timer control, interrupt control, serial communication control etc.. All types of 8051 microcontrollers, has only 21 such registers..

| SN | SFR  | NAME                | BYTE<br>ADDRESS<br>IN HEXA | SN | SFR   | NAME                         | BYTE<br>ADDRESS<br>IN HEXA |

|----|------|---------------------|----------------------------|----|-------|------------------------------|----------------------------|

| 01 | ACC* | Accumulator         | 0E0                        | 12 | IE*   | InterruptEnable              | 0A8                        |

| 02 | B*   | B register          | 0F0                        | 13 | TMOD  | Timer mode control           | 89                         |

| 03 | PSW* | Program status word | 0D0                        | 14 | TCON* | Timer control                | 88                         |

| 04 | SP   | Stack pointer       | 81                         | 15 | TH0   | Timer/counter0 high          | 8C                         |

| 05 | DPL  | Low byte            | 82                         | 16 | TL0   | Timer/counter0 low           | 8A                         |

| 06 | DPH  | High byte           | 83                         | 17 | TH1   | Timer/counter1 high          | 8D                         |

| 07 | P0*  | Port 0              | 80                         | 18 | TL1   | Timer/counter1 low           | 8B                         |

| 08 | P1*  | Port 1              | 90                         | 19 | SCON* | Serial control               | 98                         |

| 09 | P2*  | Port 2              | 0A0                        | 20 | SBUF  | SerialData buffer            | 99                         |

| 10 | P3*  | Port 3              | 0B0                        | 21 | PCON  | Power control                | 87                         |

| 11 | IP*  | InterruptPriority   | 0B8                        | 22 | PC    | Program Counter (No address) |                            |

<sup>\*-</sup> Both byte and bit ADDRESSABLE:

All SFRs such as (ACC, B, PCON, TMOD, PSW, P0 ,P1,P2,P3, ...) are accessible by name and direct address. But both of them Must be coded as direct address.

| SN | SFR   | NAME                | BYTE    | BIT     |

|----|-------|---------------------|---------|---------|

|    |       |                     | ADDRESS | ADDRESS |

|    |       |                     | IN HEXA | IN HEXA |

| 01 | ACC*  | Accumulator         | 0E0     | E7 – E0 |

| 02 | B*    | B register          | 0F0     | F7 – F0 |

| 03 | PSW*  | Program status word | 0D0     | D7 – D0 |

| 04 | P0*   | Port 0              | 80      | 87 – 80 |

| 05 | P1*   | Port 1              | 90      | 97 – 90 |

| 06 | P2*   | Port 2              | 0A0     | A7 – A0 |

| 07 | P3*   | Port 3              | 0B0     | B7 – B0 |

| 08 | IP*   | InterruptPriority   | 0B8     | BF – B8 |

| 09 | IE*   | InterruptEnable     | 0A8     | AF – A8 |

| 10 | TCON* | Timer control       | 88      | 8F – 88 |

| 11 | SCON* | Serial control      | 98      | 9F - 98 |

#### UNIT II ,unit iii & UNIT IV

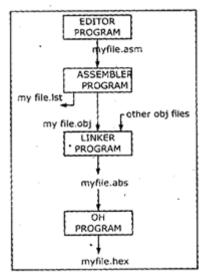

$01)\,$  a) Explain how to assemble and run an 8051 program using assembler .

(80)

### Assembling And Running an 8051 program using ASM-51

The steps to create an executable Assembly language program are outlined as follows.

(1) We use an editor to type in a program similar to program many excellent editors or word processors are available that can be used to create and/or edit the program. A widely used editor is the MS-DOS EDIT program (or Notepad in Windows).which comes with all Microsoft operating systems. The editor must be able to produce an ASCII file. For many assemblers, the file names follow the usual DOS conventions, but the source file has the extension "asm" or "src" depending on which assembler you are using.

The "asm" extension for the source file is used by an assembler in the next step.

- (2) The "asm" source file containing the program code created in step 1 is fed to an 8051 assembler. The assembler converts the instructions into machine code. The assembler will produce an object file and a list file. The extension for the object file is "obj" while the extension for the list file is "1"

- (3)Assemblers require a third step called linking. The link program takes one or more object files and produces an absolute object file with the extension "abs". This abs file is used by 8051 trainers that have a monitor program.

- (4) Next the "abs" file is fed into a program called "OH" (object to hex converter)which creates a file with extension "hex" that is ready to bum into ROM. This program comes with all 8051

assemblers. Recent Windows-based assemblers combine steps 2 through 4 into one step.

Explain different addressing modes of 8051 with examples. (08)

**ADDRESSING EXAMPLE 1 EXAMPLE 2 SLNO Immediate** MOV A,#05 MOV R4,#7AH 1 2 Register MOV A,B MOV R5,A 3 Direct ADD A,40H **MOV 40H,R0** 4 Register indirect MOV A,@R1 ADDC A,@R0 5 Indexed MOVC A,@A+DPTR MOVC A,@A+PC

#### Immediate Mode - specify data by its value

mov A, #0 ;put 0 in the accumulator ;(A) = 00000000

mov R4, #11h ;put 11hex in the R4 register ;(R4) = 00010001

mov B, #11 ;put 11 decimal in b register ; (B) = 00001011

• mov DPTR,#7521h ;put 7521 hex in DPTR ;(DPTR) = 0111010100100001

Register Addressing – either source or destination is one of CPU register

(i) MOV R0,A (ii) MOV A,R7 (iii) ADD A,R4 (iv) ADD A,R7 (v) MOV DPTR,#25F5H

(vi) MOV R5, DPL (vii) MOV R, DPH

Note that MOV R4,R7 is incorrect

<u>Direct Mode</u> – specify data by its 8-bit address . Usually for 30h-7Fh of RAM

Mov a, 70h ; copy contents of RAM at 70h to a

Mov R0,40h ; copy contents of RAM at 70h to a

Mov 56h,a ; put contents of a at 56h to a

Mov 0D0h,a ; put contents of a into PSW

<u>Register Indirect</u> – The address of the source or destination is specified in registers . Uses registers R0 or R1 for 8-bit address:

mov psw, #0 ; use register bank 0

mov r0, #0x3C

mov @r0, #3 ; memory at 3C gets #3 ; M[3C] ← 3

Uses DPTR register for 16-bit addresses:

mov dptr, #0x9000 ; dptr ← 9000h

• movx a, @dptr ; a ← M[9000] Note that 9000 is an address in external memory

<u>Register Indexed Mode</u> – source or destination address is the sum of the <u>base address</u> & the accumulator(Index)

• Base address can be <u>DPTR</u> or PC

MOV DPTR, #4000H

**MOV A, #5**

**MOVC A, @A + DPTR** ;A  $\leftarrow$  M[4005]

• BASE ADDRESS CAN BE DPTR OR <u>PC</u>

**ORG 1000H**

1000 MOV A, #5

MOVC A, @A + PC; A  $\leftarrow$  M[1008]

NOP

MOVC only can <u>read internal</u> code memory

------

#### Explain any ten Data Transfer instructions with examples

#### **DATA TRANSFER INSTRUCTIONS**

| SN | Description                                              | MN     | EMONICS       | LENGTH   |

|----|----------------------------------------------------------|--------|---------------|----------|

|    |                                                          | OPCODE | OPERANDS      | in bytes |

| 1  | Data transfer instructions move data from source         | MOV    | A,#Data       | 2        |

| 2  | operand to destination operand. source operand and       | MOV    | Data          | 3        |

| 3  | destination operand may be placed in                     | MOV    | @Ri,#Data     | 2        |

| 4  | Accumulator, internal RAM or any one of special function | MOV    | Rn,#Data      | 2        |

| 5  | registers                                                | MOV    | DPTR,#DATA    | 3        |

| 6  |                                                          | MOV    | Data addr     | 3        |

| 7  |                                                          | MOV    | Data addr     | 2        |

| 8  |                                                          | MOV    | Data addr ,Rn | 2        |

| 9  |                                                          | MOV    | Data addr,A   | 2        |

| 10 |                                                          | MOV    | @Ri,Data      | 2        |

| 11 |                                                          | MOV    | Rn,Data addr  | 2        |

| 12 |                                                          | MOV    | A, Data addr  | 2        |

| 13 |                                                          | MOV    | @Ri,A         | 1        |

| 14 |                                                          | MOV    | Rn,A          | 1        |

| 15 |                                                          | MOV    | A,@Ri         | 1        |

| 16 |                                                          | MOV    | A,Rn          | 1        |

| 17 | Data transfer between Accumulator & external memory      | MOVX   | @DPTR,A       | 1        |

| 18 |                                                          | MOVX   | @Ri,A         | 1        |

| 19 |                                                          | MOVX   | A,@DPTR       | 1        |

| 20 |                                                          | MOVX   | A,@Ri         | 1        |

| 21 | Data transfer between CY and bit address                 | MOV    | C,BIT ADDR    | 2        |

| 22 |                                                          | MOV    | BIT ADDR,C    | 2        |

| 23 | Move code byte to accumulator                            | MOVC   | A,@A+DPTR     | 1        |

| 24 |                                                          | MOVC   | A,@A+PC       | 1        |

| 25 | Retrieve from stack                                      | POP    | Data addr     | 2        |

| 26 | Push into stack                                          | PUSH   | Data addr     | 2        |

| 27 | Exchange Byte with Accumulator.Byte may be in any one    | XCH    | A, Data addr  | 2        |

| 28 | of register or internal RAM                              | XCH    | A,@Ri         | 1        |

| 29 |                                                          | XCH    | A,Rn          | 1        |

| 30 | Exchange low order bits of Byte with low order bits of   | XCHD   | A,@Ri         | 1        |

|    | Accumulator. Byte may be in any one of register or       |        |               |          |

|  |  | internal RAM |  |  |  |

|--|--|--------------|--|--|--|

|--|--|--------------|--|--|--|

Explain the instructions "ROTATE & S WAP" with example.

(80)

**SWAP:-**

**INSTRUCTION FORMAT: - SWAP A**

**FUNCTION**: Exchange Low Order 4 Bits With Upper 4 Bits Of Register A.

LENGTH: - 1B

**DESCRIPTION**: This instruction interchanges the lower 4 bits (lower nibble) with the higher 4bits (higher nibble) of A register. <u>This instruction is equivalent to four times rotate (either left or Right).</u>

EXAMPLE : MOV A,#58H ; (A) **←** 58H

SWAP A ; (A) ← 85H

**ROTATE**:- This instruction rotates the bits of Accumulator either left or Right. The bits rotated out from the Content is rotated back or front into the opposite end of the content of the accumulator.

Example: CLR C; CY  $\leftarrow$  0

MOV A, #55H; (A) **←** 01010101

|      |                             |        | , , ,    |            |      |                                    |                  |  |  |  |

|------|-----------------------------|--------|----------|------------|------|------------------------------------|------------------|--|--|--|

|      |                             |        | FLAGS    |            | AFTE | AFTER EXECUTING ROTATE INSTRUCTION |                  |  |  |  |

| SLNO | MNEMONICS                   | LENGTH | AFFECTED | EXAMPLE    | CY   | (A) - BINARY                       | (A) – HEXA       |  |  |  |

|      |                             |        |          |            |      | 01010101                           | (A) <b>←</b> 55H |  |  |  |

|      |                             |        |          | CLR C      |      |                                    |                  |  |  |  |

| 1    | RR A                        | 1B     | NONE     | MOV A,#55H | 0    | 00101010                           | 2A               |  |  |  |

|      |                             |        |          | RR A       |      |                                    |                  |  |  |  |

|      |                             |        |          | CLR C      |      |                                    |                  |  |  |  |

| 2    | RRC A 1B CARRY MOV A,#55H 1 | 1      | 00101010 | AA         |      |                                    |                  |  |  |  |

|      |                             |        |          | RRC A      |      |                                    |                  |  |  |  |

|      |                             |        |          | CLR C      |      |                                    |                  |  |  |  |

| 3    | RL A                        | 1B     | NONE     | MOV A,#55H | 0    | 10101010                           | AA               |  |  |  |

|      |                             |        |          | RL A       |      |                                    |                  |  |  |  |

|      |                             | A 1B   | CARRY    | SETB C     |      | 10101011                           |                  |  |  |  |

| 4    | RLC A                       |        |          | MOV A,#55H | 0    |                                    | AB               |  |  |  |

|      | RLC A                       |        |          |            |      |                                    |                  |  |  |  |

# Explain Various arithmetic instructions used in 8051 with suitable example. (08)

| SN | MNEMONICS |           | ADDRESSING MODE |            |                   |  |  |  |  |  |

|----|-----------|-----------|-----------------|------------|-------------------|--|--|--|--|--|

|    |           | REGISTER  | DIRECT          | INDIRECT   | IMMEDIATE         |  |  |  |  |  |

| 1  | ADD →     | ADD A,Rn  | ADD A,DIRECT    | ADD A,@Ri  | ADD A,#8BIT DATA  |  |  |  |  |  |

| 2  | ADDC →    | ADDC A,Rn | ADDC A,DIRECT   | ADDC A,@Ri | ADDC A,#8BIT      |  |  |  |  |  |

| 3  | SUBB→     | SUBB A,Rn | SUBB A,DIRECT   | SUBB A,@Ri | SUBB A,#8BIT DATA |  |  |  |  |  |

| 4  | INC A     | INC Rn    | INC DIRECT      | INC @Ri    |                   |  |  |  |  |  |

| 5  | DEC A     | DEC Rn    | DEC DIRECT      | DEC @Ri    |                   |  |  |  |  |  |

| 6  | INC DPTR  |           |                 |            |                   |  |  |  |  |  |

| 7  | MUL AB    |           |                 |            |                   |  |  |  |  |  |

| 8  | DIV AB    |           |                 |            |                   |  |  |  |  |  |

| 9  | DA A      |           |                 |            |                   |  |  |  |  |  |

Arithmetic Instructions: Source is a byte. Byte may be an any one of immediate operand (#data), register operand (Rn) or Memory content(that may be accessed by direct or indirect addressing).

| Mnemonic                            | Description            | Explanation                                                                                                                                  | Example                           | Result                     |

|-------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------|

| ADD A, byte                         | Add (A) to byte        | (A) ← (A)+byte                                                                                                                               | MOV A,#07<br>ADD A,#05            | (A) <b>←</b> 0Ch           |

| ADDC A, byte                        | Add with carry         | (A) ← (A)+byte+CY                                                                                                                            | MOV A,#56H<br>ADDC A,#0FH         | (A) <del>←</del> 65h       |

| SUBB A, byte                        | Subtract with borrow   | (A) ← (A)-byte-CY                                                                                                                            | MOV A,#07<br>SUBB A,#04           | (A) <b>←</b> 03            |

| DEC A                               | Decrement (A) by 1     | (A) ← (A)-1                                                                                                                                  | MOV A,#07<br>DEC A                | (A) <b>←</b> 0Ch           |

| DEC byte                            | Decrement byte         | (byte) ← (byte)-1                                                                                                                            | MOV R2,#A0H<br>DEC R2             | (R2)←9Fh                   |

| INC A                               | Increment (A) by 1     | (A) ← (A)+1                                                                                                                                  | MOV A,#0FH<br>INC A               | (A) <b>←</b> 10h           |

| INC byte                            | Increment byte by 1    | (byte) ← (byte)+1                                                                                                                            | MOV R3,#3FH<br>INC R3             | (R3) <b>←</b> 40h          |

| INC DPTR                            | Increment data pointer | ( DPTR)←(DPTR)+1                                                                                                                             | MOV DPTR,#422FH<br>INC DPTR       | (DPTR) <b>←</b> 4230h      |

| MUL AB                              | Multiply (A) by (B)    | <ul> <li>(A) * (B),Product is stored both registers</li> <li>A &amp; B.</li> <li>(A) ←LOB of product</li> <li>(B) ←HOB of product</li> </ul> | MOV A, #07<br>MOV B,#05<br>MUL AB | (A)←23h<br>(B) <b>←</b> 00 |

| DIV AB                              | Divide (A) by (B)      | (A) / (B), Result is in<br>(A) ←Quotient<br>(B) ←Remainder                                                                                   | MOV A, #07<br>MOV B,#05<br>DIV AB | (A)←01<br>(B) <b>←</b> 02  |

| DA A Decimal adjust the accumulator |                        | Result is in BCD                                                                                                                             | MOV A, #29H<br>ADD A,#63H<br>DA A | (A)←92<br>(BCD)            |

Write an assembly language program to perform Multibyte addition (08)

|         | INPUT |     |          |                |    |       | NPUT           |

|---------|-------|-----|----------|----------------|----|-------|----------------|

| Address | DA    | TA1 | COMMENTS | Address        |    | DATA2 | COMMENTS       |

|         | S1    | S2  |          |                | S1 | S2    |                |

| 9200    | 45    | 23  | LOB B1   | 9250           | 63 | 02    | LOB B1         |

| 9201    | 14    | 56  | ₩ B2     | 9251           | A1 | 07    | ♦ B2           |

| 9201    | 25    | 01  | HOBB3    | 9252           | 35 | FF    | HOBB3          |

|         |       |     |          | OUTPUT         |    |       |                |

| Address | DA    | ATA | COMMENTS | Set 1          |    |       | Set 2          |

|         | S1    | S2  |          |                |    |       |                |

| 9000    | A8    | 25  | LOB B1   | Data 1 : 25144 | 5  |       | Data 1: 015623 |

| 9001    | B5    | 5D  | B2       | Data2 : 35A16  | 3+ |       | Data2: FF0702+ |

MC: IMPORTANT QUESTIONS & ANSWERS | 14

| 9002 | 5A | 00 |     | В3 |             |               |

|------|----|----|-----|----|-------------|---------------|

| 9003 | 00 | 01 | НОВ | B4 | Sum: 5AB5A8 | Sum: 01005D25 |

#### **MULTIBYTE ADDITION PROGRAM:**

| LABEL | MNEMONICS                   | Description                                                       |  |  |  |

|-------|-----------------------------|-------------------------------------------------------------------|--|--|--|

|       | MOV DPTR,#9200H             | Initialise Data Pointer with data1 address                        |  |  |  |

|       | MOV R0, #35H                | Initialise R0 with internal RAM address 35h                       |  |  |  |

|       | MOV R5, #03H                | Store number of bytes in a data into R5.                          |  |  |  |

| TOP1: | MOVX A, @DPTR               |                                                                   |  |  |  |

|       | MOV @R0, A                  | Data from external memory starting at address 9200H is copied     |  |  |  |

|       | INC RO                      | into internal RAM starting at address 35H                         |  |  |  |

|       | INC DPTR                    |                                                                   |  |  |  |

|       | DJNZ R5, TOP1               |                                                                   |  |  |  |

|       | MOV DPTR, #9250H            | Initialise Data Pointer with data2 address                        |  |  |  |

|       | MOV R0, #45H                | Initialise R0 with internal RAM address 45h                       |  |  |  |

|       | MOV R5, #03H                | Store number of bytes in a data into R5.                          |  |  |  |

| TOP2: | MOVX A, @DPTR               |                                                                   |  |  |  |

|       | MOV @R0,A                   | Data from external memory starting at address 9250H is copied     |  |  |  |

|       | INC DPTR                    | into internal RAM starting at address 45H                         |  |  |  |

|       | INC RO                      |                                                                   |  |  |  |

|       | DJNZ R5, TOP2               | 7                                                                 |  |  |  |

|       | MOV DPTR, #9000H            | Initialise Data Pointer with Result address                       |  |  |  |

|       | MOV R0, #35H                | Initialise R0 with internal RAM address 35h                       |  |  |  |

|       | MOV R1, #45H                | Initialise R1 with internal RAM address 45h                       |  |  |  |

|       | MOV R5, #03H                | Store number of bytes in a data into R5.                          |  |  |  |

|       | CLR C                       | Clear A register                                                  |  |  |  |

| TOP3: | MOV A, @RO                  |                                                                   |  |  |  |

|       | ADDC A, @R1                 |                                                                   |  |  |  |

|       | /SUBB A,@R1<br>MOVX @DPTR,A |                                                                   |  |  |  |

|       | INC DPTR                    |                                                                   |  |  |  |

|       | INC DPTR                    | Multibyte data1 starting at address 9200H is added with multibyte |  |  |  |

|       |                             | data2 starting at address 9250H,Result is stored starting at      |  |  |  |

|       | INC RO                      | address 9000H                                                     |  |  |  |

|       | DJNZ R5, TOP3               |                                                                   |  |  |  |

|       | MOV A, #00H                 |                                                                   |  |  |  |

|       | JNC NXT                     |                                                                   |  |  |  |

| NIVT  | INC A                       | Check the status of CY and store the status of CY.                |  |  |  |

| NXT:  | MOVX @DPTR,A                |                                                                   |  |  |  |

| HLT:  | SJMP HLT                    |                                                                   |  |  |  |

#### List Down The Various Bit Handling Instruction Available In 8051?

| sl | MNEMONICS | length | DESCRIPTION               |  |

|----|-----------|--------|---------------------------|--|

| 1. | CLR C     | 1B     | Clear the carry bit       |  |

| 2. | CLR BIT   | 2B     | Clear th e indicated bit. |  |

| 3. | SET C     | 1B     | Set the carry flag.       |  |

| MC   | • | IMPORTANT |  |

|------|---|-----------|--|

| IVIC | • |           |  |

| 4.  | SET BIT     | 2B | Set the indicated bit.                                                        |  |

|-----|-------------|----|-------------------------------------------------------------------------------|--|

| 5.  | CPL C       | 1B | Complement the carry flag.                                                    |  |

| 6.  | CPL BIT     | 2B | Complement the indicated bit.                                                 |  |

| 7.  | MOV C, BIT  | 2B | The value of the indicated bit is transfer to carry flag.                     |  |

| 8.  | MOV BIT,C   | 2B | The value of the carry flag is transfer to indicated bit.                     |  |

| 9.  | ANL C,BIT   | 2B | Logical ANDing the carry flag with the indicated bit value.                   |  |

|     |             |    | Result is placed in carry.                                                    |  |

| 10. | ANL C,/BIT  | 2B | Logical ANDING carry flag with the complement of the indicated bit value.     |  |

|     |             |    | Result is placed in carry.                                                    |  |

| 11. | ORL C,BIT   | 2B | Logical ORING carry flag with the indicated bit .                             |  |

|     |             |    | Result is placed in carry.                                                    |  |

| 12. | ORL C,/BIT  | 2B | Logical ORING the carry flag with the complement of the indicated bit. Result |  |

|     |             |    | is placed in carry.                                                           |  |

| 13. | JC REL      | 2B | Jump to relative address when carry=1                                         |  |

| 14. | JNC BIT,REL | 2B | Jump to relative address when carry=0                                         |  |

| 15. | JB BIT,REL  | 3B | Jump to relative address if the indicated bit = 1                             |  |

| 16. | JNB BIT,REL | 3B | Jump to relative address if the indicated bit = 0                             |  |

| 17. | JBC BIT,REL | 3B | Jump to relative address if the indicated bit = 1 and clear the bit.          |  |

|     |             |    |                                                                               |  |

|     | •           |    |                                                                               |  |

#### **Explain the following instruction** CJNE Instruction.

**Instruction Format**: CJNE dest-byte, source-byte, target

**Description**: The magnitudes of the source byte and destination byte are compared. If they are not equal, it jumps to the target address. Notice that the target address can be no more than 128 bytes backward or 127 bytes forward, since it is a 2-byte instruction.

CJNE jumps only for the not-equal value. To find out if it is greater less after the comparison, we must check the CY flag. After CJNE instruct affects the CY' flag only and after the jump to target address the carry flag indicates which value is greater, as shown here.

(i)Dest < Source CY = 1 (ii) Dest> Source CY = 0

This instruction supports four addressing modes. In two of them, A is the destination

1. Immediate: CJNE A, # data, target address

Example: CJNE A, #96, NEXT; JUMP IF A is not 96

2. Direct: CJNE A, direct, target address

Example: CJNE A, 40H, NEXT; JUMP IF A NOT= With the Value Held By RAM LOC.

3. Register: CJNE Rn, #data, target

Example: CJNE R5, #70, NEXT; JUMP if R5 is not 70

4. Indirect: CNJE @Ri, # data, target

Example: CJNE @R1, #80, Next; Jump if RAM Location whose address is held by R1 is

not equal to 80

------

#### **Explain DJNZ Instruction**

**Instruction Format:** DJNZ Byte, Target

**Meaning:** Byte is decremented, and if the result is not zero it will jump to target address.

**Example:** DJNZ R2, BACK; repeat if R2 not = zero

The following two fomats are supported by this instruction.

1. Register: DJNZ Rn, target (where n=0 to 7)

Ex: DNJZ R3, HERE; repeat if R3 not = zero

2. Direct: DJNZ direct, target

Use of DJNZ (Looping Program): Repeating a sequence of instructions a certain number of times is called a loop. The loop is one of most widely used actions that any microprocessor performs. In the **8051**, the loop action is performed by the instruction 'DJNZ reg, Label". In this instruction, the register is decremented if it is not zero, it jumps to the target address referred to by the label. Prior to the start of the loop the regsiter is loaded with the counter for the number of repetitions.

\_\_\_\_\_\_

Explain the logical instructions with example.

**BYTE LEVEL LOGICAL OPERATION(Byte operands)** The following are the byte level operations. They use all four addressing modes for the source of a data byte. The A register or direct address in internal RAM is the destination of logical operation result. Note that no flags are affected by the byte level logical operations unless the direct RAM address is the PSW .

| SN | MNEMONICS         | RESULT STORED | ADDRESSING MODE        |              |           |                     |  |

|----|-------------------|---------------|------------------------|--------------|-----------|---------------------|--|

|    |                   | IN            | REGISTER               | DIRECT       | INDIRECT  | IMMEDIATE           |  |

| 1  | ANL →             | ACCUMULATOR   | ANL A,Rn               | ANL A,DIRECT | ANL A,@Ri | ANL A, #8BIT DATA   |  |

| _  | , J               | INTERNAL RAM  |                        | ANL DIRECT,A |           | ANL DIR, #8BIT DATA |  |

| 2  | ORL →             | ACCUMULATOR   | ORL A,Rn               | ORL A,DIRECT | ORL A,@Ri | ORL A, #8BIT DATA   |  |

| _  | J. 12             | INTERNAL RAM  |                        | ORL DIRECT,A |           | ORL DIR, #8BIT DATA |  |

| 3  | XRL →             | ACCUMULATOR   | XRL A,Rn               | XRL A,DIRECT | XRL A,@Ri | XRL A, #8BIT DATA   |  |

|    | 72                | INTERNAL RAM  |                        | XRL DIRECT,A |           | XRL DIR, #8BIT DATA |  |

| 4  | CPL A ACCUMULAT   |               | COMPLEMENT ACCUMULATOR |              |           |                     |  |

| 5  | CLR A ACCUMULATOR |               | CLEAR ACCUMULATOR      |              |           |                     |  |

Logical Instructions: Source is a byte. Byte may be an any one of immediate operand(#data), register operand (Rn) or Memory content(that may be accessed by direct or indirect addressing).

| Mnemonic     | Description                              | Explanation                   | Example                      | Result              |

|--------------|------------------------------------------|-------------------------------|------------------------------|---------------------|

| ANL A, byte  | Logical AND (A) with byte                | (A) ← (A)^byte                | MOV A,#07<br>ANL A,#05       | (A) <b>←</b> 05h    |

| ANL DIR,BYTE | Logical AND content of IRAM with BYTE    | (IRAM) ← (IRAM)^BYTE          | MOV 45h,#56H<br>ANL 45h,#0FH | ((45)) <b>←</b> 06h |

| ORL A, byte  | Logical OR (A) with byte                 | (A) ← (A) v (byte)            | MOV A,#07<br>ORL A.#05       | (A) <b>←</b> 07h    |

| ORL DIR,BYTE | Logical ORing content of IRAM with BYTE  | (IRAM) ← (IRAM) v (BYTE)      | MOV 45h,#56H<br>ORL 45h,#0FH | ((45))←5Fh          |

| XRL A, byte  | Logical XOR (A) with byte                | (A) ← (A)+(byte)              | MOV A,#07<br>XRL A,#05       | (A) <b>←</b> 02h    |

| XRL DIR,BYTE | Logical XORing content of IRAM with BYTE | (IRAM) ← (IRAM) ¥ (BYTE)      | MOV 45h,#56H<br>XRL 45h,#0FH | ((45))←59h          |

| CPL A        | COMPLEMENT (A)                           | (A) ← COMPLEMENT OF (A)       | MOV A,#3FH<br>CPL A          | (A)←C0h             |

| CLR A        | CLEAR (A)                                | ( A)← (00000000) <sub>2</sub> | MOV A,#42H<br>CLR A          | (A) <b>←</b> 00h    |

| SNO | MNEMONICS     | DESCRIPTION                                                                                                                 |  |

|-----|---------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| 1   | ANL A,#N      | AND each bit of A with the same bit of immediate number 'N'. Put the result in A                                            |  |

| 2   | ANL A, DIRECT | AND each bit of A with the same bit of the direct RAM address. Put the result in A                                          |  |

| 3   | ANL A, Rr     | AND each bit of A with the same bit of Register Rr. Put the result in A                                                     |  |

| 4   | ANL A,@RP     | AND each bit of A with the same bit of the content of RAM address contained in RP.  Put the result in A                     |  |

| 5   | ANL DIRECT,A  | AND each bit of A with the same bit of the direct RAM address. Put the result in direct RAM address.                        |  |

| 6   | ANL DIRECT,#N | AND each bit of the direct RAM address with the same bit of immediate number 'N'. Put the result in the direct RAM address. |  |

| 7   | ORL A,#N      | OR each bit of A with the same bit of immediate number 'N'. Put the result in A                                             |  |

| 8   | ORL A, DIRECT | OR each bit of A with the same bit of the direct RAM address. Put the result in A                                           |  |

| 9   | ORL A, Rr     | OR each bit of A with the same bit of Register Rr. Put the result in A                                                      |  |

| 10  | ORL A,@RP     | OR each bit of A with the same bit of the content of RAM address contained in RP.                                           |  |

| 10  | ONL A, WINI   | Put the result in A                                                                                                         |  |

| 11  | ORL DIRECT,A  | OR each bit of A with the same bit of the direct RAM address. Put the result in                                             |  |

|     |               | direct RAM address.                                                                                                         |  |

| 12  | ORL DIRECT,#N | OR each bit of the direct RAM address with the same bit of immediate number 'N'.  Put the result in the direct RAM address. |  |

| 13  | XRL A,#N      | XOR each bit of A with the same bit of immediate number 'N'. Put the result in A                                            |  |

| 14  | XRL A, DIRECT | XOR each bit of A with the same bit of the direct RAM address. Put the result in A                                          |  |

| 15  | XRL A, Rr     | XOR each bit of A with the same bit of Register Rr. Put the result in A                                                     |  |

| 16  | XRL A,@RP     | XOR each bit of A with the same bit of the content of RAM address contained in RP.                                          |  |

|     | 727.4,6 1     | Put the result in A                                                                                                         |  |

| 17  | XRL DIRECT,A  | XOR each bit of A with the same bit of the direct RAM address. Put the result in                                            |  |

|     | ·             | direct RAM address.                                                                                                         |  |

| 18  | XRL DIRECT,#N | XOR each bit of the direct RAM address with the same bit of immediate number                                                |  |

| 19  | CPL A         | 'N'. Put the result in the direct RAM address .  COMPLEMENT (A). Every one becomes zero. Every zero becomes one.            |  |

|     |               |                                                                                                                             |  |

| 20  | CLR A         | CLEAR CONTENT OF ACCUMULATOR.                                                                                               |  |

#### Explain I/O programming with example.

- In 8051, I/O devices should be treated as memory.

- So memory mapped I/O is only possible for accessing I/O devices.

- MOVX instructions are used for accessing both memory and IO devices.

- By using bit manipulation instructions, we can perform various functions like clear,set,complement,AND,OR, move and control jump in bit level.

- Example: Write an ALP for receiving data in a port pin P2.0 and store it in memory location 2FH

| LABEL | Mnemonics  | Description                                   |

|-------|------------|-----------------------------------------------|

|       | SETB P2.0  | Set the port pin P2.0 ,make P2.0 as input pin |

|       | MOV C,P2.0 | Move the bit data inP2.0 to Carry             |

|       | MOV 2FH,C  | Store the data in bit location 2FH            |

| I 11 T. | I CIMID LIT |  |

|---------|-------------|--|

| L   .   | JUNIT LIFT  |  |

Explain Time delay routines with examples.

Delay routines are subroutines used for maintaining the timing of various operations in 8051.

- o In some applications, certain operations are repeated after a specified time interval.

- o In Control applications, certain equipment is needed to be ON/OFF after a specified time delay.

- In such cases, Delay routines can be used to maintain the timing of operations.

Example: Delay program with one loop:

| Mnemonics |              | No of m/c | No of times         | Total No of    |

|-----------|--------------|-----------|---------------------|----------------|

| Label     | Commands     | cycles    | executed            | machine cycles |

| Delay:    | MOV RO,#0FFH | 1         | 1                   | 1              |

| LOOP:     | DJNZ RO,LOOP | 2         | (255) <sub>10</sub> | (500)10        |

|           | RET          | 2         | 1                   | 2              |

|           |              |           | TOTAL               | (503)10        |

- (assume XTAL frequency = 11.0592MHz)

- Total time period produced by this subroutine = 503 \* 1.085microsecond.

- This delay subroutine can produce a maximum delay of 545 microsecond.

#### What is the difference between the flags CY and OV.

This flag is set whenever the result of a signed number operation is too large, causing the highorder bit to overflow into the sign bit. In general, the carry flag is used to detect errors in unsigned arithmetic operations. The overflow flag is only used to detect errors in signed arithmetic operations.

------

#### Write an ALP to convert a hexa decimal to its equivalent BCD number.

(80)

| LABEL | MNEMONICS        | COMMENT                                            |

|-------|------------------|----------------------------------------------------|

|       | MOV DPTR, #4150h | INITIALIZE DPTR WITH INPUT ADDRESS 4150H.          |

|       | MOVX A, @DPTR    | (A) ← INPUT DATA AT ADDRESS 4150H.                 |

|       | MOV B, #64H      | TO FIND OUT NUMBER OF 100'S IN A GIVEN DATA, IT IS |

|       | DIV AB           | DIVIDED BY 100(64H).                               |

|       | MOV DPTR, #4250H | QUOTIENT IS STORED AT ADDRESS 4250H                |

|       | MOVX @DPTR, A    |                                                    |

|       | MOV A, B         | REMAINDER IS MOVED TO A REGISTER                   |

|       | MOV B, #0AH      | TO FIND OUT NUMBER OF 100'S IN A GIVEN DATA, IT IS |

|       | DIV AB           | DIVIDED BY 10(0AH).                                |

|       | INC DPTR         | QUOTIENT IS STORED AT ADDRESS 4251H                |

|       | MOVX @DPTR, A    |                                                    |

|       | INC DPTR         | REMAINDER IS MOVED TO A REGISTER AND STORED AT     |

|       | MOV A, B         | ADDRESS 4252H                                      |

|       | MOVX @DPTR, A    |                                                    |

| LABEL  | MNEMONICS       |              |      | COV     | /MENT   |       |    |          |            |

|--------|-----------------|--------------|------|---------|---------|-------|----|----------|------------|

| HLT:   | SJMP HLT        |              |      |         |         |       |    |          |            |

|        | INPUT           |              |      |         |         |       |    | OU       | TPUT       |

| ADDRES | SS              | DATA1 COMMEN |      | NTS     | ADDRESS | DATA2 |    | COMMENTS |            |

|        |                 | S1           | S2   |         |         |       | S1 | S2       | RESULT BCD |

| 445011 |                 |              | 25   | DATA IN |         | 4250  | 02 | 00       | 100'S      |

| 4150H  | 4150H   FF   25 |              | HEXA |         | 4251    | 05    | 03 | 10'S     |            |

|        |                 |              |      |         |         | 1252  | ΛF | 07       | 1'C        |

\_\_\_\_\_

#### Explain the format of IE & IP register.

(80)

#### Format of IE register.

MC: IMPORTANT

- a) 8 bit register. Register Address **0A8h**

- b) interrupt enable register.(byte/bit addressable register)

- c) To enable/disable All of the interrupts in 8051,we make high/low in the bit **EA of** the IE register .

- d)To enable/disable any one of the interrupts,we make the corresponding bit in the IE register high/low.

| ←8bit |      |      |      | IE   |      |      |      |

|-------|------|------|------|------|------|------|------|

| Bit7  | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| EA    |      |      | ES   | ET1  | Ex1  | ET0  | EX0  |

| Bit | Bit | function              | Bit | Bit | Function                       |

|-----|-----|-----------------------|-----|-----|--------------------------------|

| 7   | EA  | Enable all interrupts | 3   | ET1 | Timer 1 interrupt enable       |

| 6   |     |                       | 2   | EX1 | External interrupt 1 interrupt |

| 5   |     |                       | 1   | ET0 | Timer 0 interrupt enable       |

| 4   | ES  | Serial port interrupt | 0   | EX0 | External interrupt01 interrupt |

Format of IP register: a) 8 bit register.

b) interrupt priority register.

(byte/bit addressable register)

| <ul><li>c) Upon reset</li></ul> | , IP register contains all | 0's. |

|---------------------------------|----------------------------|------|

|---------------------------------|----------------------------|------|

| ←8bit IP |      |      |      |      |      |      |      |

|----------|------|------|------|------|------|------|------|

| Bit7     | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|          |      |      | PS   | PT1  | Px1  | PT0  | PX0  |

d) With the use of IP register, user may change the priority. d) To give a higher priority to any of the interrupts, we make the corresponding bit in the IP register high.

| Bit no | Bit name | Function    | Bit no | Bit | Function                                |

|--------|----------|-------------|--------|-----|-----------------------------------------|

| 7      |          |             | 3      | PT1 | Timer 1 interrupt priority              |

| 6      |          |             | 2      | PX1 | External interrupt 1 interrupt priority |

| 5      |          |             | 1      | PT0 | Timer 0 interrupt priority              |

| 4      | PS       | Serial port | 0      | PX0 | External interrupt0 interrupt priority  |

Explain External interrupts with suitable program.

[08]

#### PROGRAMMING EXTERNAL HARDWARE INTERRUPTS

The 8051 has two external hardware interrupts. Piri 12 (P3.2) and pin 13 (P3.3) of the 8051, designated as INTO and INT1, are used as external hardware interrupts. Upon activation of these pins, the 8051 gets interrupted in whatever it is doing and jumps to the vector table to perform the interrupt service routine. In this section we study these two external hardware interrupts of the 8051 with some examples.

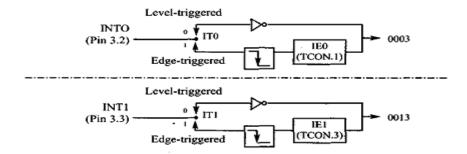

Figure A. Activation of INTO and INT1 External interrupts INTO and INT1

There are only two external hardware interrupts in the 8051: INTO and INT1. They are located on pins P3.2 and P3.3 of port 3, respectively. The interrupt vector table locations 0003H and 0013H are set aside for INTO and INT1, respectively. They are enabled and disabled using the IE register. There are two types of activation for the external hardware interrupts: (1) level triggered, and (2) edge triggered.

#### Level-triggered interrupt

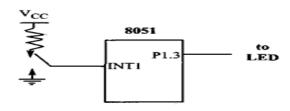

In the level-triggered mode, INTO and INT1 pins are normally high (just like all I/O port pins) and if a low-level signal is applied to them, it triggers the interrupt. Then the microcontroller stops whatever it is doing and jumps to the interrupt vector table to service that interrupt. This is called a *level-triggered* or *level-activated interrupt* and is the default mode upon reset of the 8051. The low-level signal at the INT pin must be removed before the execution of the last instruction of the interrupt service routine, RETI; otherwise, another interrupt will be generated. In other words, if the low-level interrupt signal is not removed before the ISR is finished it is interpreted as another interrupt and the 8051 jumps to the vector table to execute the ISR again. Assume that the INT1 pin is connected to a switch that is normally high. Whenever it goes low, it should turn on an LED. The LED is connected to PI .3 and is normally off. When it is turned on it should stay on for a fraction of a second. As long as the switch is pressed low, the LED should stay on.

```

оооон

ORG

MAIN

;bypass interrupt vector table

LJMP

hardware

interrupt INT1

to turn on the

ISR

ORG

0013H

;INT1

SETB

P1.3

on LED

;turn

MOV

R3,#255

:load

counter

DJNZ

LED on for

BACK:

R3, BACK

:keep

a while

LED

CLR

off

the

P1.3

;turn

RETI

from

:return

; -- MAIN program

initialization

ORG

зон

IE,#10000100B

MAIN:

MOV

enable external

INT1

SJMP

HERE:

HERE

;stay here until

interrupted

END

```

Pressing the switch will turn the LED on. If it is kept activated, the LED stays on.

\_\_\_\_\_\_

Write an assembly language program to generate a square wave of 5 KHz on port pin 1.5 using timer mode 2. Assume crystal frequency to be 11.0592 MHz. (08)

Crystal frequency = 11.0592 MHz: Frequency to timer = 11.0592 MHz / 12 = 921.6 KHzClock period to timer = (1/921.6 KHz) = 1.085 microsecond

a) in Hex T = Time delay = (FF - XX +1) x 1.085 microsecond

where XX are TL initial value. Notice that value XX is in hex.

**b)** in decimal: Convert XX value of the TL register to decimal to get a NNN decimal number, then T = Time delay = (256 - NNN) x 1.085 microsecond

#### Programming Steps to generate a time delay using the timer's mode 2

- T = 1/5 KHz = 0.2 ms

- 1/2 of it for the high and low portions of the pulse = 0.1ms

- $0.1 \text{ ms} / 1.085 \,\mu\text{s} = 92.1659$

- 256 92.17 = 163.84 = 164(approximately) in decimal = 0A4H

- TL1 = TH1 = 0A4H

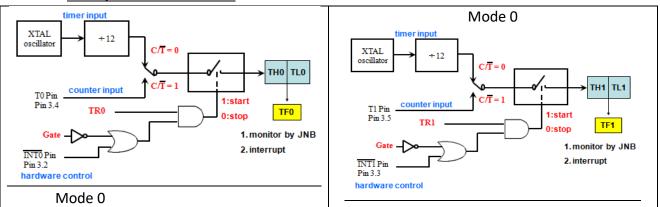

# In programming the 8051 to generate a time delay using the timer's mode 2,

the following steps must be taken.

- 1) The TMOD register is loaded with the value indicating which timer(timer 1 or timer 0) and which mode is selected.( mode 2: 8 -bit Auto Reload timer/counter).

- 2) The THx and TLx is loaded with the initial value for the desired time delay. (assuming XTAL=11.0592 MHz)

| MOV TH0,#XX | Initialise TH0 with initial value. |

|-------------|------------------------------------|

| MOV TH1,#XX | Initialise TH1 with initial value. |

- 3) Start the timer. **SETB TR0**: Start timer 0. & **SETB TR1**: Start timer 1.

- 4) The TFx flag bit is monitored with the use of the following instruction to see if TIMER overflow is occurred. "wait: JNB TF0, wait" (for Timer 0)

and "wait: JNB TF1, wait" (for Timer 1)

5) Clear the timer overflow flag. **CLR TFO**; To Clear timer overflow flag 0.

**CLR TF1**; To Clear timer overflow flag 1.

- 6) Stop the timer. **CLR TRO**: To Stop timer 0. And **CLR TRO**: To Stop timer 0.

- 7) go to step 3 since it is auto reload(for mode 2, no need to initilaise the value).

#### **PROGRAM:** To generate a square wave at P1.5 using timer 0 in mode 2.

|      |        | <u> </u>      |                                                  |

|------|--------|---------------|--------------------------------------------------|

| Step | Label  | Mnemonics     | Comments                                         |

| 1    |        | MOV TMOD,#02H | ; timer 0, mode 2 (8 BIT auto reload)            |

| 2    |        | MOV TH0,#0A4H | ; Initialise TH0 with initial value for timer 0. |

| 3    | Again: | CPL P1.5      | Complement P1.5                                  |

| 4    |        | SETB TRO      | ; start timer 0                                  |

| 5    | HERE:  | JNB TF0,HERE  | ;monitor timer 0 overflow flag.                  |

| 6    |        | CLR TRO       | ;stop the timer 0                                |

| 7    |        | CLR TF0       | ;TF0 is cleared for next round                   |

| 8    |        | SJMP Again    | ;repeat the process                              |

### **PROGRAM:** To generate a square wave at P1.5 using timer 1 in mode 2.

| Step | Label  | Mnemonics     | Comments                                                             |

|------|--------|---------------|----------------------------------------------------------------------|

| 1    |        | MOV TMOD,#20H | ; timer 1, mode 2 (8 BIT auto reload)                                |

| 2    |        | MOV TH1,#A4H  | ; Initialise TH1 with initial value for timer 1.                     |

| 3    | Again: | CPL P1.5      | Complement P1.5                                                      |

| 4    |        | SETB TR1      | ; start timer 1                                                      |

| 5    | HERE:  | JNB TF1,HERE  | ;monitor timer 1overflow flag.                                       |

| 6    |        | CLR TR1       | ;stop the timer 1                                                    |

| 7    |        | CLR TF1       | ;TF1 is cleared for next round                                       |

| 8    |        | SJMP Again    | ;repeat the process [ since it is auto reload(for mode 2, no need to |

#### **PROGRAM ( USING TIMER INTERRUPTS):**

Program to generate a square wave at P1.5 using timer 0 in mode 2.

| Step | Label  | Mnemonics         | Comments                                                                                    |  |  |

|------|--------|-------------------|---------------------------------------------------------------------------------------------|--|--|

| 1    |        | MOV TMOD,#02H     | ; timer 0, mode 2 (8 BIT auto reload)                                                       |  |  |

| 2    |        | MOV IE,#10001010B | ; B- BINARY. Enable timer interrupts.(both TF0 & TF1)                                       |  |  |

| 3    |        | MOV TH0,#0A4H     | ; Initialise TH0 with initial value for timer 0.                                            |  |  |

| 4    | Again: | CPL P1.5          | Complement P1.5                                                                             |  |  |

|      |        | SETB TR1          | ; start timer 1                                                                             |  |  |

| 6    | HERE:  | JNB TF0,HERE      | ;monitor timer 0 overflow flag.                                                             |  |  |

| 7    |        | SJMP Again        | ;repeat the process.[ since it is auto reload(for mode 2, no need to initilaise the value). |  |  |

| ISR  | 000Bh  | CLR TRO           | ;stop the timer 0 Vector address is 000Bh                                                   |  |  |

| 1    |        | CLR TF0           | ;TF0 is cleared for next round                                                              |  |  |

| 2    |        | RETI              | Return from ISR [ Interrupt Service Routine ]                                               |  |  |

#### **PROGRAM ( USING TIMER INTERRUPTS):**

Program to generate a square wave at P1.5 using timer 1 in mode 2.

| Step | Label  | Mnemonics         | Comments                                                     |  |  |  |

|------|--------|-------------------|--------------------------------------------------------------|--|--|--|

| 1    |        | MOV TMOD,#20H     | ; timer 1, mode 2 (8 BIT auto reload)                        |  |  |  |

| 2    |        | MOV IE,#10001010B | ; B- BINARY. Enable timer interrupts.(both TF0 & TF1)        |  |  |  |

| 3    |        | MOV TH1,#A4H      | ; Initialise TH1 with initial value for timer 1.             |  |  |  |

| 4    | Again: | CPL P1.5          | Complement P1.5                                              |  |  |  |

| 5    |        | SETB TR1          | ; start timer 1                                              |  |  |  |

| 6    | HERE:  | JNB TF1,HERE      | ;monitor timer 1overflow flag.                               |  |  |  |

| 7    |        | SJMP Again        | ;repeat the process [ since it is auto reload(for mode 2, no |  |  |  |

| ISR  | 001Bh  | CLR TR1           | ;stop the timer 1 Vector Address is 001Bh                    |  |  |  |

| 1    |        | CLR TF1           | ;TF1 is cleared for next round                               |  |  |  |

| 2    |        | RETI              | Return from ISR [ Interrupt Service Routine ]                |  |  |  |

We can develop a formula for delay calculations using **MODE 1 (16-BIT) OF THE TIMER** for a crystal frequency of XTAL= 11.0592 MHz. This is given in calculation.

Crystal frequency = 11.0592 MHz: Frequency to timer = 11.0592 MHz / 12 = 921.6 KHzClock period to timer = (1/921.6 KHz) = 1.085 microsecond

#### a) in Hex

T = Time delay = (FFFF - YYXX +1) x 1.085 microsecond

where YYXX are TH, TL initial values respectively. Notice that values YYXX are in hex.

**b)** in decimal: Convert YYXX values of the TH, TL register to decimal to get a NNNNN decimal number, then T = Time delay = (65536 - NNNNN) x 1.085 microsecond

#### Programming Steps to generate a time delay using the timer's mode 1

- T = 1/50 Hz = 20 ms